Carry Adder

5 stars based on

57 reviews

Carry Adder Are you looking for?: Hi All I need to add a bit signal to a bit signal, and it won't generate carry bit. Since the clock is really fast, I'm trying to figure out how complex the adder logic might be, based on standard library from TSMC.

For example, 16 bit ripple carry adder vhdl codes the critical path have more than 21 NAND-like level of combo cells?

Can some body shed lights on ho. Design a bit mutiplier. How many MOS transistors are required to implement full adder? Hai, I am trying to implement full adder logic with the below 10 transistors circuit. I am using nm technology.

16 bit ripple carry adder vhdl codes am getting sum values properly. But observing some voltage degradation with respect to the carry values. Full adder standard cell layout. Just draw a single bit full adder and connect in ripple carry style by 16 bit ripple carry adder vhdl codes three more copies of it I am assuming it is a school project.

Net has unmapped pin s. The tool is likely reporting that it dropped the carry out of the addition. Hobby Circuits and Small Projects Problems:: Carry skip adder error in VHDL. Please recompile with -mt off -v 1 swi.

Carry-in of Error Tolerant Adder. Any helps would be highly appreciated, thanks. The generate will assign to temp. Is there a type of adder faster than carry look ahead adder? I want to know ALL the different type of arithmatic circuits used in digital circuit design arranged per speed.

Here I am talking about adder s and multipliers. As far as I know the subtractor is merely created from the adder itself by merely using 2s complete of the second operand. I am not aware of any adder faster than the I am trying to build carry increment adder in VHDL, but getting some error.

Need help with 8bits accumulator using 4bits adder. I need to construct an 8-bit accumulator. For this, I need an 8-bit adder.

But my ASIC vendor? So I construct the accumulator. When I synthesized the circuit, I found that there was a max-delay violation on the? To correct this, I added Can anyone look into the code and suggest corrections? Hi, I need a verilog code for 16bit signed carry look ahead adderPlease help me.

Parallel MAC unit design problems. Detail how you implemented and differences from expected. Hi everyone hope you are all fine. I am new here please help me. Carry skip adder- doubt regarding two parameters. Are the adder width and the block size same for a carry skip adder? Help needed with ripple carry adder! Ugh, what is with the poor formatting of code from new users? Plz can any one send me VHDL code for the following bit adder s: It can be generalized as below.

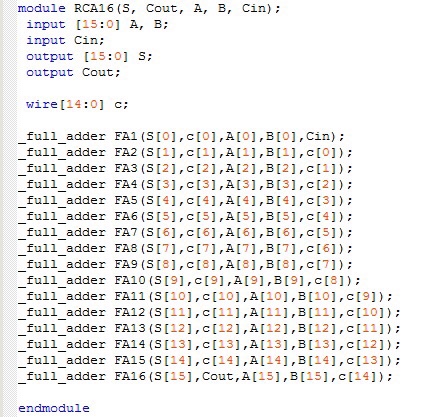

Ripple Carry Adder using Structural Modeing. ALL; entity ripple is Port x: Here is 16 bit ripple carry adder vhdl codes more formal definition. A ripple carry adder 16 bit ripple carry adder vhdl codes implemented purely with a half- adder and multiple full adder s. There is pretty much only one way to implement this type What are you exactly asking? A don't care specification will usually reflect a redundant part of the logic function. Hopefully the design compiler will utilize it to minimize resource usage or achieve other performance objectives, e.

A full adder will only fit into a single logic cell, if carry in and out are available f. Modular 8 bit Ripple Carry Adder Help! I am trying to build a ripple carry adder using a hierarchical verilog structure description.

What I have is not working right My logic is messed up somewhere but not sure where. I grabbed the test bench from a 8 bit multiplier to use for the RCA and so I know I am overlooking something basic HSpice taking too much time to simulate stopped at some point. Hi to all Am simulating one four bit ripple carry adder having four full adder s. In simulation, its taking too much time to respond literally stopping at the 16 bit ripple carry adder vhdl codes full adder.

When i remove one full adder and connect one half adder its working fine. Please clarify this to me. Software Problems, Hints and Reviews:: Square root carry select adder.

Hi, Can anyone direct me to the vhdl library for a half adderfull adder and a carry -look-ahead adder please? CLA with 9-bits Or in any other case, a suggestion for designing them. Triggering a Combinational Logic module from a 16 bit ripple carry adder vhdl codes Logic module. I am having a separate module for the 4 bit ripple carry adder. I have tested the adder module and it works fine. Using a Compressor for column compression 16 bit ripple carry adder vhdl codes dadda multiplier.

Hello I am designing a dadda multiplier and i am doing its column compression using a and Compressors. Can somebody help me by telling which stage the couts and carry go to in this compression scheme. As in a compressor has 2 carry in and 2 carry out and a carry which stage do they belong: My code has successful simulation and synthesis,which used ripple carry adder. Manchester Carry Chain Sizing.

Hi all, I would like to ask you a question about a simple, I think problem that I haven't been able to solve. I am trying to improve my knowledge of adder blocks so, while studying from the Rabaey,Chandrakasan - "Digital Integrated Circuits", I run into an interesting example about how to size a Manchester carry Chain represented in the figure. Can't get binary adder IC to work. Hello, I'm working on a calculator as a little hobby and I'm having an issue with the binary adder IC that I have.

I have everything wired according to the datasheet yet, no matter what I do to the inputs, all 4 of the sum and carry Out outputs only put out as high. I cannot get them to turn off, let alone add correctly. I've tried switching out. Hello Guys, Let me first apologize if this is in the wrong section, but I need to implement a 4-bit adder on a transistor level circuit and implement a layout representation of it as part of a project. I've been doing some reading and the Manchester carry Chain adder looked a good prospect as a result of the lower number of transistors Previous 1 2 3 4 Next.