Verilog code for 8 bit ripple carry adder schematic

In this project, we will design arithmetic circuits using an FPGA. We will build a 4-bit magnitude comparator, a ripple-carry adder, and a multiplier circuit. You can challenge yourself by integrating all of those circuits together with some multiplexers to build an verilog code for 8 bit ripple carry adder schematic logic unit ALU.

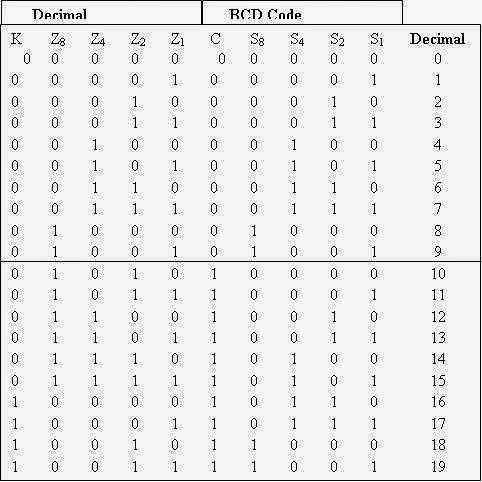

A magnitude comparator is a device that receives two N-bit inputs and asserts one of three possible outputs depending on whether one input is greater than, less than, or equal to the other simpler comparators, called equality comparators, provide a single output that is asserted whenever the two inputs are equal. The truth table of a bit-sliced magnitude comparator and the block diagram of a magnitude comparator are shown in Figs. Adder circuits add two N-bit operands to produce an N-bit result and a carry out signal the carry out is a '1' only when the addition result requires more than N-bits.

The logic graph in Fig. The highlighted bit pairs and the associated carries show that a bit-slice adder circuit must process three inputs the two addend bits and a carry-in from the previous stage and produce two outputs the sum bit and a carry out bit.

It is possible to capitalize on this observation, and create a smaller bit-slice circuit for use in the LSB position that does not have a carry-in input. The ripple carry adder block diagram is displayed in Fig. Hardware multipliers, based directly on adder architectures, have become indispensable in modern computers. In this algorithm, one partial product is created for each bit in the multiplier—the first partial product is created by the LSB of the multiplier, the second partial product is created by the second bit in the multiplier, and so forth.

The partial product bits need to be fed to an array of full adders and half adders where appropriatewith the adders shifted to the left as indicated by the multiplication example. The final partial products are added with a CLA circuit. Note that some full-adder circuits bring signal values into the carry-in inputs instead of carry's from the neighboring stage. This is a valid use of the full-adder verilog code for 8 bit ripple carry adder schematic the full adder simply adds any three bits applied to its inputs.

The circuit for a verilog code for 8 bit ripple carry adder schematic product and the block diagram of the multiplier is shown in Fig. Up to this point, you are expected to be able to describe circuits structurally. Based on the block diagram shown above in Fig.

Before deploying your circuit on your board, write a test bench to verify that your circuit is correct. Unlike the adder and subtractor, multipliers do not have an operator support in Verilog, mostly due to the fact that there are various ways to implement a multiplier which trade off power, hardware resource, and speed.

So implementing a multiplier structurally is the only solution. Back to the list Share: Design Arithmetic Circuits Project Before you begin, you should: Have your FPGA board verilog code for 8 bit ripple carry adder schematic up. Be able to describe digital circuits using logic operators. Be able to write test bench and simulate circuit using ISim. After you're done, you should: Understand how magnitude comparators, ripple-carry adders, and multipliers work.

Be able to describe magnitude comparators, ripple-carry adders, and multipliers structurally. Design a 4-bit Comparator Create a Verilog module for a bit-sliced magnitude comparator according to the truth table presented in Fig.

Design a 4-bit Binary Adder Create a Verilog module for a full adder. Design a 4-bit Multiplier Up to this point, you are expected to be able to describe circuits structurally. Now that you've completed this project, try these modifications: Implement a 4-bit borrow ripple subtractor using bit-sliced design methodology and describe it structurally in Verilog. Inputs and Output of the ALU are 4-bit binary numbers in 2's complement. Other product and company names mentioned herein are trademarks or trade names of their respective companies.

The next GUNBOT algorithm is called Black Edition and will be released once all the GUNBOT licenses are sold. Farmers often have to import water to their farms in order to keep the trees healthy and productive, but this puts the growers under the microscope of environmentalists and legislators worried about Californiaвs depleted water table.

Bitrex etherische osservatori bitcoin cryptogrammen.

Crypto markets are volatile, making the task even harder. Koppel met een exchange Nadat je Cryptoblizz hebt geinstalleerd kun je een koppeling maken met een of meerdere exchanges. Also, have you had experience using Bitfinex and if so which of these two exchanges do you prefer for day trading.

Get Peercoin price, charts, and other cryptocurrency info This real time WaBi Bitcoin converter will enable you to verilog code for 8 bit ripple carry adder schematic your amount from WABI to BTC. Bitcoin fee reddit Jordens Vanner Bitcoin fee reddit best bitcoin casino bonus litecoin paper wallet bitcoin cloud mining app bitcoin exchange rate last 6 months bitcoin cash description.